µBGA またはマイクロ BGA またはマイクロ ボール グリッド アレイは、最新かつ最先端の表面実装デバイスの 1 つと考えられており、PCB 設計者向けのパッケージにすぐに変身します。 マイクロ ボール グリッド アレイは、一般的な BGA のサブカテゴリです。 BGA パッケージの一般的なボール間の間隔は 0.8 mm ~ 1.0 mm の範囲ですが、マイクロ BGA の一般的なパッケージのピッチは 0.4 mm の範囲であるか、これより小さい場合もあります。 ただし、これによりパッケージのサイズが最小限に抑えられます。 さらに、マイクロ BGA は PCB の表面に非常に近接して配置することもできます。

パッケージング技術は、デバイスの性能において重要な役割を果たします。 ここ数年、高度な技術により、実際の集積回路半導体物質におけるチップの遅延は減少しました。 ただし、パッケージのICでは信号遅延はあまり低減できません。 したがって、パッケージは高速性能デバイスの不可欠な部分になります。 マイクロ BGA は、とりわけ理想的なソリューションとして機能します。 他のテクノロジーよりも大きなチップ遅延アクティビティが可能になるためです。

μBGA(マイクロボールグリッドアレイ)欠陥検査

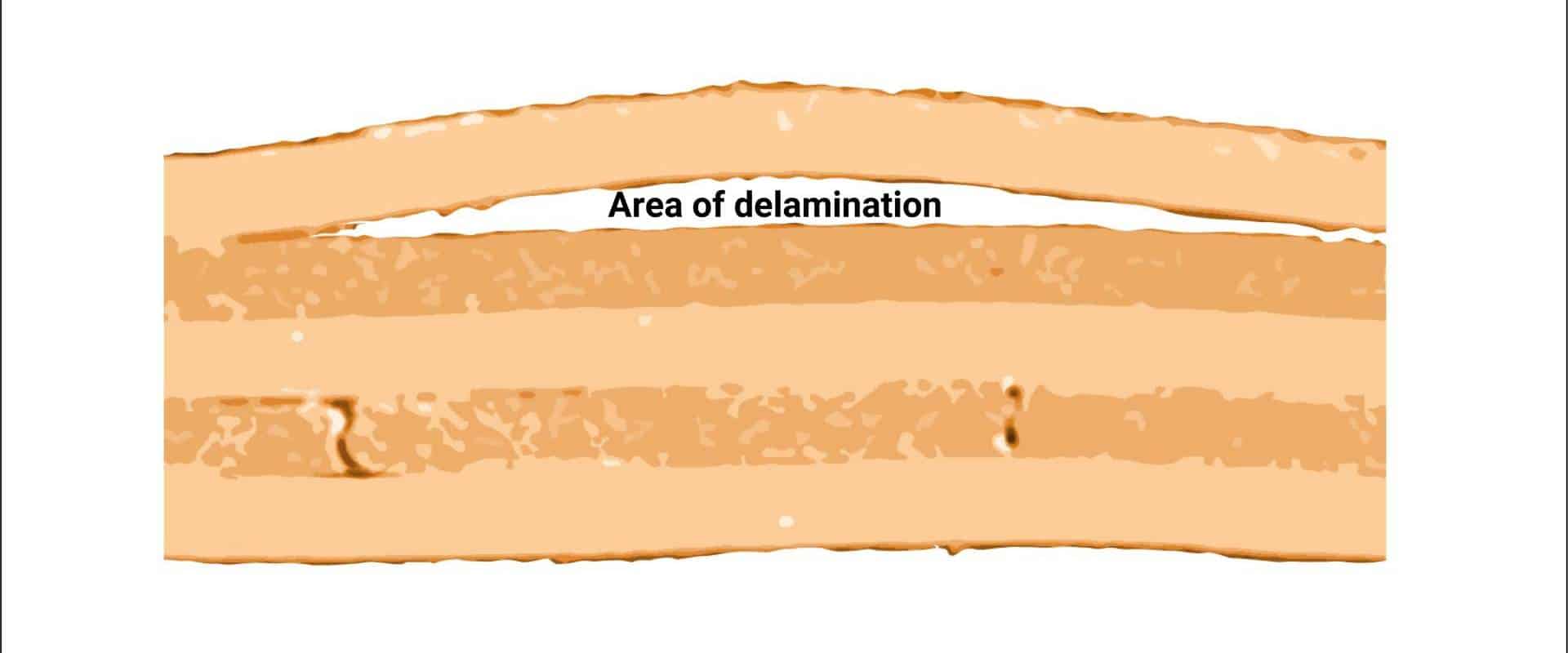

はんだ付けプロセス後、BGA のコンポーネントを簡単に検出できます。 ただし、コンポーネント、機器、はんだ付けプロセス、および環境問題によって欠陥が発生する可能性があります。 これらの欠陥には、開回路、コールドはんだ付け、短絡、ブリッジング、はんだ付け損失、位置ずれなどが含まれる場合があります。 それにもかかわらず、BGA はんだボールには、ボールの欠落やサイズの不均一などの欠陥問題が含まれる場合があります。

BGA検査では最終製品の品質を判断することが難しい場合があります。 これは、BGA のはんだボールが外観検査とチップの下に配置されているという事実に関連しています。 ただし、これでははんだ接合部に存在する空洞を示すことはできません。 したがって、検査には高品質の結果が得られる専門的で洗練された検査装置が必要です。 このような高度な方法には、境界スキャン、X 線検査、電気試験などが含まれます。

従来の電気試験方法は、短絡回路や断線回路を検出するのに最適であることが証明されています。 バウンダリースキャンははんだ接合部へのアクセスに役立ちますが、そこでバウンダリーコネクタと呼ばれる接続が行われます。 これにより、接続された SMD コンポーネントの短絡および断線を検査できます。 バウンダリスキャンの方法では、電気的テストよりも目に見えない接合部のテストも可能になります。 どちらも基板の電気的性能と導通を検査するのに効果的であることが証明されています。 ただし、はんだの品質検査はできません。 したがって、はんだの品質だけでなく、隠れた接合部や目に見えない接合部に存在するはんだを見つけるのに役立つ他の方法をこれらのテクノロジに組み込む必要があります。

X 線装置による方法では、BGA PCB の組み立て中に生じるその他の欠陥も検査されます。 X線検査により、はんだボールやペーストのブリッジなどのはんだ付けの問題が排除されます。 ただし、一部の X 線装置には、はんだボールのガオ サイズを簡単に計算できるソフトウェア サポートが含まれています。 ただし、これにより、X 線装置が標準セットに準拠している必要があります。 2D X 線装置は、BGA の内層、冷間はんだ接合部、ブラインド ビア、およびはんだ接合部上のビアを分析するための 3D 画像を生成するのに役立ちます。

µBGA (マイクロ ボール グリッド アレイ) の利点

他の表面実装デバイスと比較して、µBGA パッケージの構造が複雑なため、デバイスのピンと外界との間の接触長さが短くなります。 ただし、各信号に低インピーダンスとインダクタンスの経路が与えられます。 ロジック実装のテクノロジーと集積回路半導体の進歩に合わせて、パッケージの密度を高め、パッケージングプロセスの遅延を減らすことで、信号の損失を最小限に抑えます。

µBGA の電気的性能は、それがリンゴであるか、短いリード線の抵抗、インダクタンス、およびキャパシタンスであることを表します。 高性能デバイスの場合、追加のグランド プランにより、相互インダクタンス、自己インダクタンス、およびクロストークが最小限に抑えられます。

一方、マイクロ BGA は、PCB レイアウトに大きな課題をもたらすため、コンポーネントのパッケージングにおける大きな進歩を示しています。 一般的なマイクロまたはμBGAパッケージは0.4mmのピッチで構成されますが、高度なクリアピッチBGAは0.25mmや0.3mmなどのより小さなピッチで提供されます。 PCB の設計者は、BGA ピッチ 0.4mm でのピン配線のためのより簡単な方法とソリューションを見つける必要があります。 そうしないと、配線が複雑になる可能性があります。 最終的に、これらの複雑さにより層数が増加し、製造プロセスの高い要件が求められます。 これは、設計者が microBGA パッケージのデザインを使用する前に、microBGA のデバイスの詳細を注意深く分析する必要があることを意味します。 また、ボールのピン ピッチにより、製造上の不要な特別な要件を使用せずに、すべての配線の配線が可能になります。 さらに、このプロセスは、必要な層数内で実行できます。

ただし、これは、設計者が、パフォーマンスをインポートせずに、より多くのピン数のパッケージを配線するために必要な層数を最適化したいことを示しています。 さらに、ピンの接地と microBGA の割り当てを簡単に変更して、最適な数の基板層とともに効率的な配線を可能にすることができます。

μBGA (マイクロ ボール グリッド アレイ) の NSMD および SMD パッド

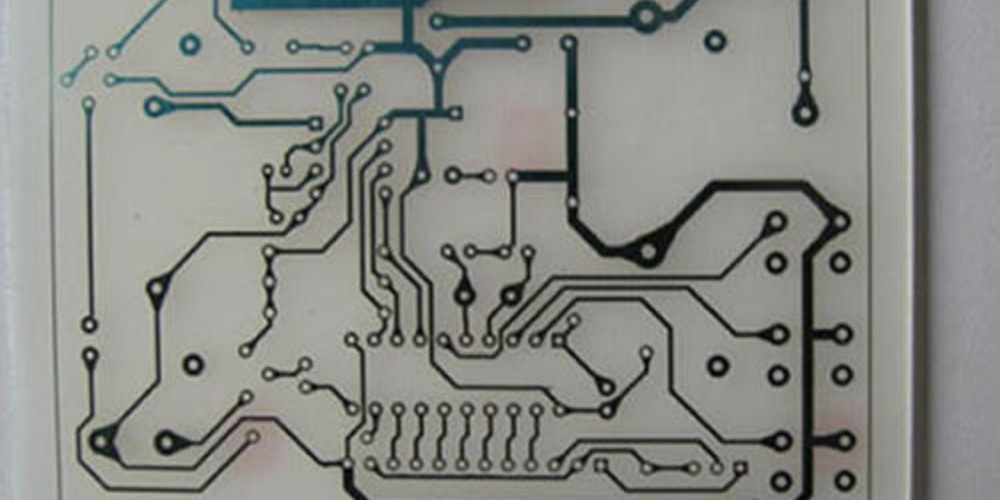

チップのメーカーは、ランド パターンからなる詳細な情報シートを提供しています。 BGA パッドには通常 2 種類の表面パターンがあります。 はんだマスク定義または SMD パッド、および非はんだマスク定義または NSMD パッド。

NSMD パッドにははんだマスクの開口部が含まれています。 これらの開口部はパッドに比べて大きいです。 同時に、SMD パッドにははんだマスクの開口部が含まれています。 これらの開口部は、銅のパッドに比べて小さく見えます。 ほとんどのサプライヤーは、ソルダーマスクの位置公差のプロセスよりも銅のアートワークレジストレーションをより強力に制御できる NSMD の使用を推奨しています。 したがって、PCB 設計者が µBGA パッケージなどのクリアピッチ コンポーネントを扱う場合、これはさらに重要になります。

PCB 設計における µBGA (マイクロ ボール グリッド アレイ)

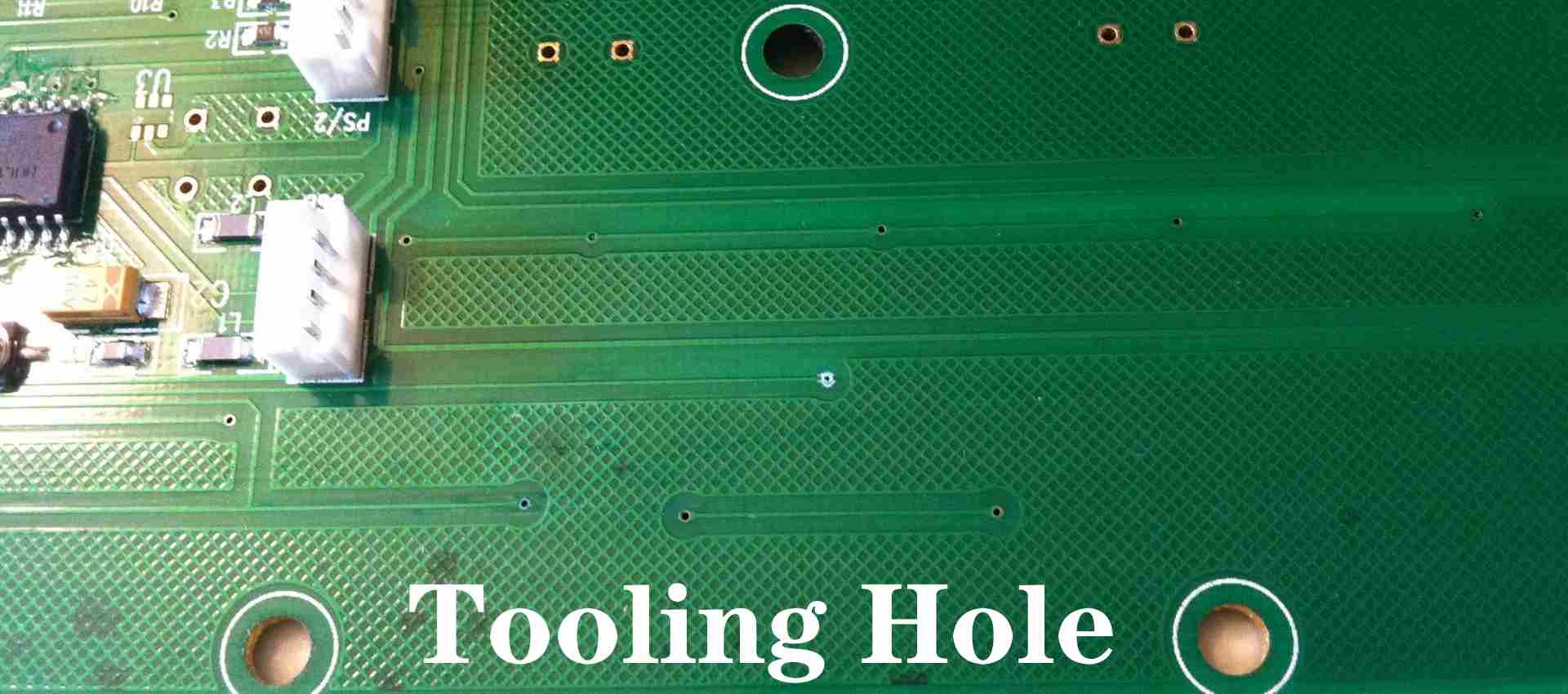

配線またはファンアウト技術では、表面の直径、ボール ピッチ、ビアの種類、パッドのサイズ、層数、トレースの間隔または幅、マイクロ BGA から離れるために必要な入出力ピンの数などのいくつかの側面が考慮されます。

従来のドッグボーン配線パターンはマイクロ BGA には適切ではないようです。 これにより、埋め込み/ブラインド ビアまたはパッド内ビアの必要性が高まります。 ビアインパッドの方法では、デバイスのコンタクトパッドの下に直接ビアを置きます。 これらのビアには、導電性の銅または銀などの他の導電性材料が充填されています。 したがって、平坦な表面が得られます。 これにより、配線が改善され、コンポーネントの密度が高まります。

これは、BGA 配線の従来の方法がここでは機能しないことを明確に示しています。 これは、メーカーが埋め込み/ブラインド ビアまたはパッド内ビア、あるいはその両方を使用する必要があることを意味します。 ただし、PCB の製造プロセスを本当にコスト効率よく行いたい場合は、埋め込みビアやブラインド ビアを使用しないでください。 ただし、実際にはマイクロ BGA のサイズとピンの配置に基づいています。

マイクロ BGA のパッケージにより、設計の複雑さがさらに高まります。 パッケージの狭いピッチは、従来の BGA よりもコンパクトな領域の設計内に多数のコンポーネント ピンを配置するため、PCB の設計にさまざまな課題を引き起こします。 同様に、基板の製造にも高度な技術と方法を経る必要があり、コストが増加します。 PCB メーカーは、このような種類のコンポーネント用の PCB の簡単な製造プロセスを作成する必要があり、ピッチ コンポーネントの配置を考慮する必要があります。

マイクロ BGA は、さまざまな物理的および電気的利点を提供します。 さらに、他のテクノロジーと同様に、マイクロ BGA にも問題がないわけではありません。 たとえば、マイクロ BGA のような専門知識を簡単に、または一般的に見つけることはできません。 再加工の方法はより複雑になる一方、はんだ接合部の信頼性はさらに重要になります。 さらに、ボイドの問題が急速に深刻化している一方で、マイクロ BGA の組立検査も困難になっています。