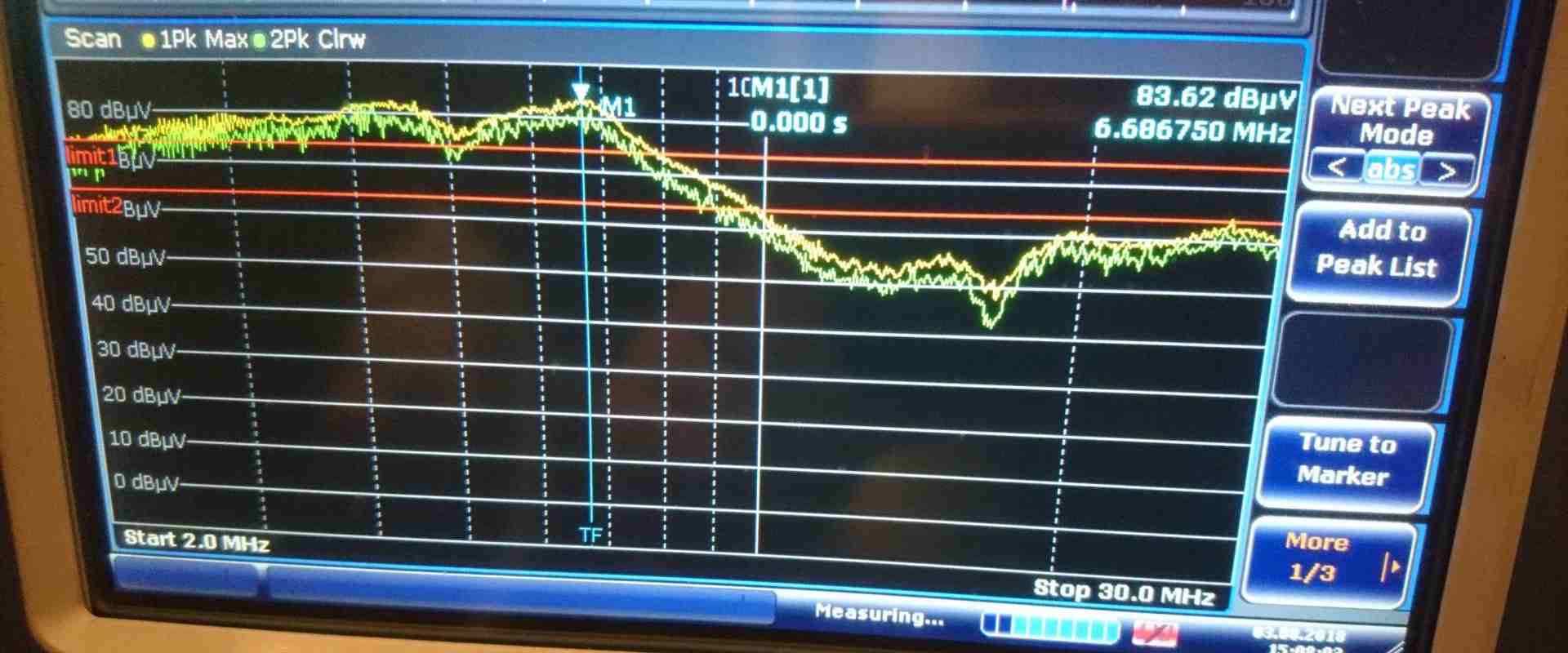

PCB 設計者は電磁波の問題に頻繁に直面するため、システム設計エンジニアは電磁干渉と互換性を継続的に監視する必要があります。 残念ながら、設計上の軽微な問題が電磁的な問題を引き起こす可能性があり、基板設計が縮小し、顧客が高速化を要求するにつれて、電磁的な問題はこれまで以上に蔓延しています。

主な懸念事項が 2 つあります。

電磁両立性 (EMC) および電磁妨害 (EMI)。 EMC は電磁エネルギーの生成、送信、受信に関連しており、多くの場合、不適切な設計によって引き起こされます。 一方、EMI は、EMC および外部電磁源からの干渉による有害で望ましくない影響を指します。 過度の EMI は、製品の欠陥や損傷を引き起こす可能性があります。 EMI の影響を軽減するには、PCB 設計者は EMC 設計ガイドラインに従う必要があります。

幸いなことに、適切な EMC 設計によって回路基板の EMI を低減できます。

PCB における EMI 問題の種類

EMI は次の 2 つのタイプに分類できます。

・広範囲のEMI

・狭帯域EMI

限られた周波数範囲内で狭帯域 EMI が発生する可能性があり、場合によっては 1 つの周波数だけで発生することもあります。 ラジオ、携帯電話、テレビ局はこのタイプの EMI の発生源としてよく知られており、断続的または継続的に発生する可能性があります。 狭帯域 EMI は破壊的ではありますが、通常、機器に損傷を引き起こすことはありませんが、広帯域 EMI は損傷を引き起こします。 ブロードバンド EMI はさらに広範囲に広がり、電子機器に損害を与える可能性があります。 モーター、蛍光灯の故障、車の点火、電線の故障、ジェットエンジンなど、さまざまな原因が原因で発生する可能性があります。 広帯域 EMI は、電子機器の意図した信号に干渉します。

広範囲の周波数で発生する EMI は、最も頻繁に発生する無線周波数によって引き起こされることがよくあります。 雷、送電線、回路、ランプ、その他の発生源は、この種の干渉を引き起こすエネルギーを放出する可能性があります。

電子機器が正しく機能しない場合、このタイプの EMI が発生している可能性があります。 家庭環境では、電子機器に軽度の干渉を引き起こすだけかもしれませんが、産業部門ではハードウェアの損傷、データの損失、生産性の低下を引き起こす可能性があります。

EMIの発生源

EMI を発生させる可能性のある発生源には次のものがあります。

· EMIの自然発生源

落雷、静電気、宇宙ノイズ、太陽フレアと塵、大気電気、吹雪、太陽などの自然発生源は、この種の EMI を引き起こす可能性があります。

適切に保護されていない場合、この EMI は軍用機器や輸送システムなどの電気機器に突然影響を与えます。 吹雪によって発生するような弱い EMI は、電話信号を妨害する可能性があります。

・住宅用EMI

ワイヤレス デバイスや電子機器も、この EMI のよく知られた発生源です。 この種の EMI は通常、永久的な損失を引き起こすことはありませんが、それでも他の電子機器の機能を妨害し、損なう可能性があります。

Wi-Fi デバイス、ラップトップ、携帯電話、電子レンジ、Bluetooth デバイス、ベビーモニター、オーブントースター、その他多くの電子機器は住宅用 EMI を引き起こす可能性があります。 家に余分な電子機器を追加すると、潜在的な EMI 発生源の数が増加します。

電子機器の品質も人為的な EMI に影響を与える可能性があります。 より高い性能レベルと動作周波数を備えた電子機器は、EMI を発生するリスクがより高くなる可能性があります。

・産業用

この形式の EMI は大規模に発生するか、重大な干渉を引き起こす可能性があります。 この種の EMI の発生源はさまざまです。 これらには、電気モーターや発電機、電話や携帯電話のネットワーク、衛星通信、ラジオやテレビ、鉄道、送電網、医療機器などが含まれます。

PCB 業界における EMI シールドの重要性

これは、繊細な電子レイアウトを干渉から保護し、より強力な信号が近くの電子機器を妨害するのを防ぐために非常に重要です。 プリント基板設計チェックリストは、どのコンポーネントを保護する必要があるか、また効果的に保護する方法を思い出すのに役立ちます。

EMI は、個人用電子機器から産業用電子機器、緊急システムや重要な軍事に至るまで、さまざまな分野の繊細な電子機器に影響を与える可能性があります。 したがって、電気システムを EMI からシールドするためにあらゆる手段を講じることが重要です。

PCB、シールドにおける EMI 問題とは何ですか?また、その仕組みは何ですか?

EMI シールドには、EMI の原因となる可能性のある放射線や電磁信号の吸収から回路を保護するシールドで回路を覆うことが含まれます。

EMI シールドは干渉を減衰し、シールドの金属内に電流の流れを生成します。 次に、それは接地基準面に向けられます。

PCB の EMI シールド

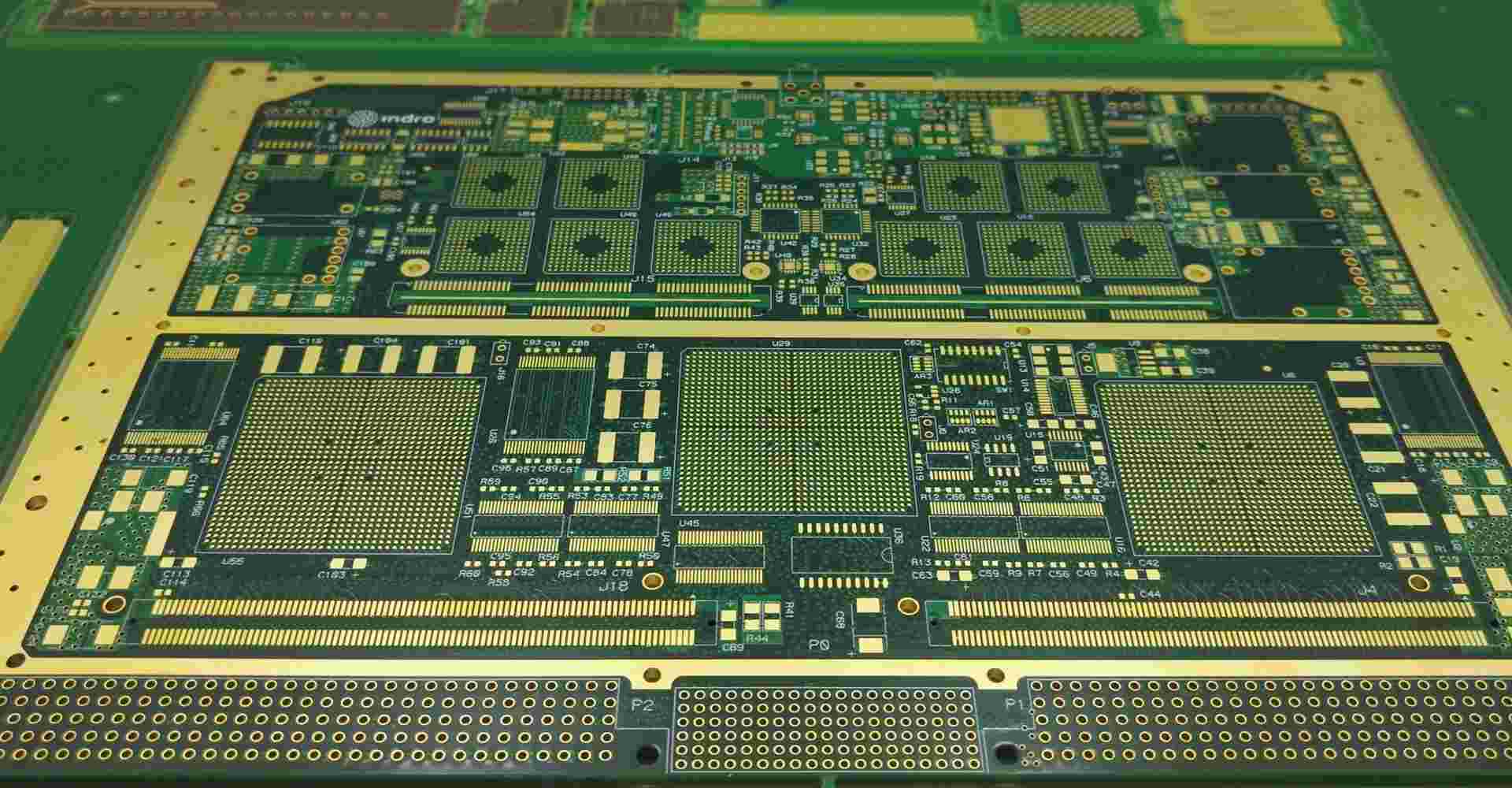

プリント基板のシールドは、医療、軍事、通信などのさまざまな用途に使用されています。 出力、入力、アンプなど、EMI の影響を最も受けやすいステップに実装されることがよくあります。

回路基板の典型的な問題を防ぐには、回路基板を放射線や EMI 吸収から保護できる金属シールドでシールドすることが不可欠です。 これを実現するために、回路とコンポーネントは他のボードから分離可能です。

PCB における EMI 問題: 設計原則

EMI を低減するには、PCB 設計者は電磁適合性レイアウト原則に従う必要があります。 EMC 問題の主な原因は通常、トレース、PCB コイル、ビア、回路、その他のコンポーネント間の干渉を引き起こす設計欠陥に起因します。 これらの重要な設計の基本を組み込むことは、PCB 設計における電磁気問題の防止と対処に役立ちます。

1. グランドプレーン

PCB のグランド プレーンの作成は、電磁干渉 (EMI) を最小限に抑える上で不可欠かつ重要なステップです。 すべての回路が正しく機能するにはグランドが必要であるため、グランド プレーンは EMI に対する主な保護です。 EMI を低減するには、環境を設計するために次のような効果的な方法がいくつか推奨されています。

グランド領域を最大化する: エミッション、ノイズ、クロストークを最小限に抑えるには、プリント基板内のグランド領域を可能な限り増やして最大化することをお勧めします。 これにより、信号がより簡単に分散され、パフォーマンスが向上します。 グランドプレーンが不十分な場合、考えられる解決策の 1 つは、追加の層を追加するか、多層プリント基板を生成することです。 これにより、高周波トレースの処理がより柔軟になります。

ソリッド プレーンの使用: 特に多層プリント基板の場合は、ソリッド グランド プレーンを強くお勧めします。 銅泥棒またはエッチングされたグランド プレーンは抵抗レベルが高くなる傾向がありますが、壊れていないグランド プレーンはインピーダンス レベルが低くなります。

各コンポーネントを接続する: グランド基準面が回路基板設計の緩衝剤となるように、すべての要素をグランド プレーンとポイントに接続することをお勧めします。 フローティングコンポーネントは、グランドプレーンの利点を十分に活用できません。

スプリットプレーン: 複雑な PCB 設計では、複数の安定化された電圧が必要になることが多く、それぞれにグランド プレーンが必要です。 ただし、多くの接地基準面を組み込むと、製造コストが上昇する可能性があります。 この問題に対処するには、分割プレーンが役立ちます。 単一のレイヤー上に複数の地面パーツを作成できるようになります。 ただし、設計者は、必要な場合にのみ、パーティション分割されたプレーンを慎重に使用する必要があります。 スプリット プレーンを実装する場合、ループの作成を避けるためにそれらを 1 点で接続することが重要です。 その結果、アンテナから EMI が放射される可能性があります。

バイパスの接続: バイパス コンデンサとデカップリング コンデンサが設計の一部である場合、それらをグランド プレーンに接続することが重要です。 そうすることでループ サイズが小さくなり、グランド電流が減少します。

信号の長さ: 信号がソースへ、またはソースから送信されるまでにかかる時間を一定にする必要があるため、トレースの長さは重要な要素です。 そうしないと、EMI 放射が発生します。 これを最小限に抑えるために、トレース (配線) の長さを短くし、サイズがほぼ同じになるようにすることをお勧めします。

2. トレースのレイアウト

トレースは電流を正しく伝播するため、基板設計において非常に重要です。 ただし、パスが EMC レイアウトの最上位ルールに従って順序付けされていない場合、多くの問題が発生する可能性があります。

トレースは、回路がアクティブなときに流れる電子を運ぶ導電性経路です。 したがって、設計に 1 つの間違いがあると、放射アンテナに変わってしまう可能性があります。 トレースの曲がりや交差などの単純な箇所であっても、プリント基板の電磁干渉を引き起こす可能性があります。

プリント基板設計における配線レイアウトに関する推奨ルールをいくつか示します。

直角を避ける: プリント基板の設計では、トレース、ビア、または追加部品では 45 ~ 90 度の角度を避けることをお勧めします。 パスの角度が 45 度を超えると、静電容量が増加する傾向があります。 これにより、特性インピーダンスが変化し、その後の反射が発生します。 反射により EMI が発生する可能性があります。 これを防ぐために、コーナーを曲がる必要があるトレースは、丸くするか、45 度以下の角度で 2 回以上曲がる必要があります。

信号を分離する: 干渉を防ぐために、動きの速い信号パスを動きの遅い信号パスから離して維持することをお勧めします。 また、アナログ信号をデジタル信号から遠ざけてください。 これらの信号が近接すると、干渉が発生する可能性があります。

戻り経路を短くする: 干渉を最小限に抑えるには、電流が戻る経路を短くし、最小の抵抗の経路に沿って電流を戻すことが重要です。 リターン パスの長さは、送信トレースとほぼ同じか、さらに短くすることをお勧めします。

心の間隔: デュアル高速信号が互いに並行して実行されると、クロストークとして知られる現象を通じて電磁干渉 (EMI) が発生する可能性があります。 したがって、ここでは、痕跡の 1 つは「攻撃者」と呼ばれ、もう 1 つは「被害者」と呼ばれます。 さらに、アグレッサー トレースは、キャパシタンスとインダクタンスを誘導および結合することでビクティム トレースに影響を与え、ビクティム トレースに逆方向電流と順方向電流の両方を生成します。

クロストークを減らすために、配線間の最小距離を維持することをお勧めします。 通常、間隔はパスの幅の少なくとも 2 倍にする必要があります。 たとえば、パスの幅が 5 ミルの場合、2 つの平行なトレース間の最小距離が 10 ミル以上であることを確認します。

ビアは慎重に使用してください。PCB 設計者は、トレース時に基板内のさまざまな層の利点を活かすためにビアを使用します。 ただし、ビアはキャパシタンスとインダクタンスの影響を与えるため、慎重に使用する必要があります。 信号強度の変化により、信号の跳ね返りが発生する可能性があります。 ビアによりトレースが長くなるので、バランスを取る必要があります。 差動配線は、可能であればビアを介して配線しないでください。 やむを得ない場合は、両方の導電パスにビアを使用して遅延を調整します。

3. コンポーネントの配置

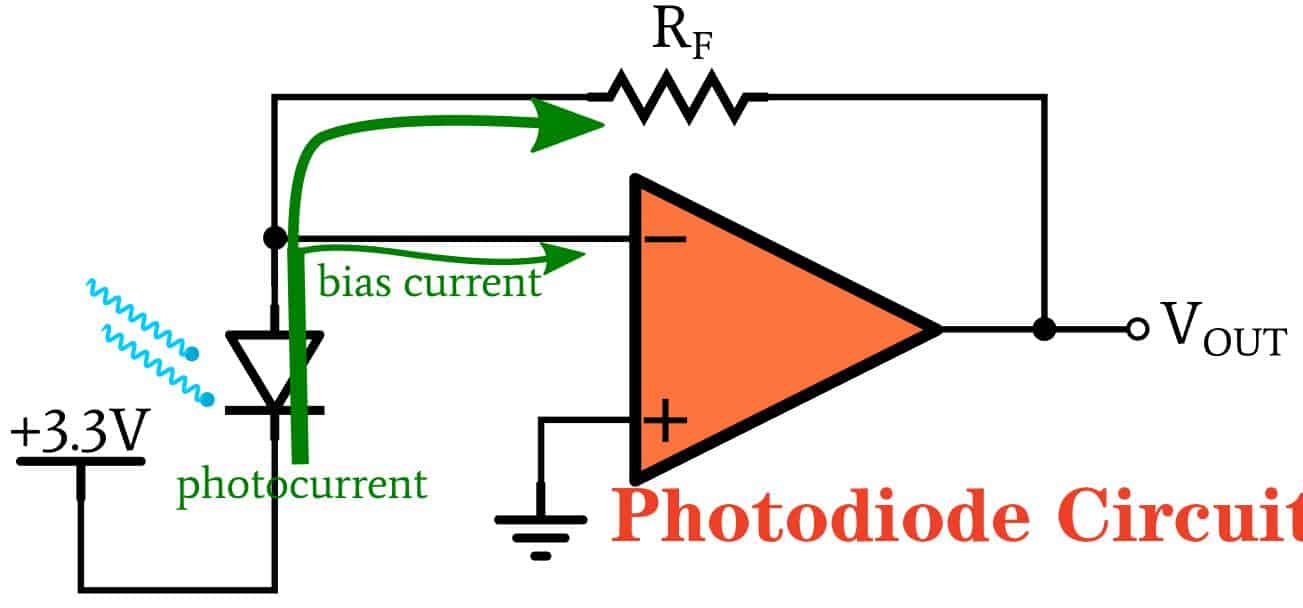

電子回路における EMI 問題を防ぐには、電子部品を適切に配置することが重要です。 プリント基板を設計する際には、各部品の EMI の影響を考慮することが重要です。 プリント基板設計における要素レイアウトの効果的な実践例は次のとおりです。

アナログ部品とデジタル部品を分離する: クロストークやその他の問題を防ぐには、配線の分離と同様に、PCB 設計においてデジタル回路とアナログ回路またはコンポーネントを分離しておくことが不可欠です。 近接して配置すると干渉が発生する可能性があります。 これを回避するために、設計者は複数の層、シールド、および個別のグランドを使用して、デジタル信号とアナログ信号を分離することができます。 多くの場合、それらを完全に別々のグランドプレーンに置くことをお勧めします。

個別のアナログ部分と高速部分: アナログ回路には通常、大電流が流れます。 高周波トレースやスイッチング信号に問題が発生する可能性があります。 これらの回路を互いに分離し、グランド信号を使用してアナログ回路をシールドすることが重要です。 多層 PCB では、アナログ配線を配線して、アナログ回路基板と高周波信号の間にグランド基準面を作成することをお勧めします。

高速コンポーネント: 電子コンポーネントが小さくて高速であるほど、かなりの量の EMI が発生する可能性が高くなります。 これに対処するには、シールドまたはフィルタリング技術を実装することをお勧めします。 さらに、基板設計ではこれらの要素を他の要素から分割することが重要です。 もう 1 つの戦略は、高周波信号とクロックをできるだけグランド プレーンに隣接させて配置することです。これにより、クロストーク、放射レベル、ノイズを最小限に抑え、許容範囲内に保つことができます。

4. EMIシールド

準拠する設計ルールに関係なく、特定のコンポーネントは必然的に電磁干渉 (EMI)、小型および高速ユニットを生成します。 ただし、この EMI の影響は、シールドとフィルタリングによって軽減できます。 さまざまなシールドおよびフィルタリング技術が利用できます。そのうちのいくつかは次のとおりです。

コンポーネントと基板のシールド: 回路基板の全体または一部を囲むために使用できる物理的保護として知られる金属パッケージ。 その主な目的は、電磁干渉 (EMI) の侵入を防ぐことです。基板の電気接続と、この目的を達成するために使用される方法は、EMI の発生源によって異なります。 EMI がシステムから発生する場合、要素/コンポーネント シールドは、EMI を生成する特定のコンポーネントをカプセル化することができます。

このアース接続により、アンテナ ループのサイズが小さくなり、EMI が吸収されます。 外部 EMI 源から保護するために、他のタイプのシールドで回路基板全体を覆うこともできます。 ファラデー ケージは、RF 波を妨げる厚い保護筐体の一例です。 通常、金属と導電性フォームが使用されており、これらのシールドはこの目的に役立ちます。

ローパス フィルター: 場合によっては、プリント基板にハイカット フィルターを組み込んで、素子から発せられる高速ノイズを除去することができます。 これらのフィルターは 3 つの部分からのノイズを抑制し、戻り時に電流が妨げられることなく流れるようにします。

ケーブルのシールド: EMI の問題は、アナログ電流とデジタル電流の両方を伝送するケーブルで最も顕著です。 これらのケーブルは、特に高速信号の場合、寄生容量と寄生インダクタンスを生成します。 ただし、これらのケーブルを絶縁し、両端で接地すると、EMI 干渉を排除できます。

結論

電子機器は EMI により重大な誤動作が発生する可能性があります。 したがって、プリント基板を作成するときは、システムの最適なパフォーマンスを保証するためにどのシールド方法が最適であるかを慎重に検討することが重要です。