フィールド プログラマブル ゲート アレイ (FPGA) は、ザイリンクスの中核製品ラインです。 製造後にプログラムおよび再プログラムできる半導体デバイスです。 FPGA は、航空宇宙および軍事、自動車、産業オートメーション、データセンターおよびネットワーキング、有線および無線通信などのさまざまなアプリケーションで役立ちます。

FPGA に加えて、ザイリンクスは、Vivado Design Suite、SDx 開発環境、PetaLinux ツールなどの設計および開発ソフトウェア ツールを提供しています。 同社の IP コアは、接続、メモリ インターフェイス、ビデオおよび画像処理、セキュリティなどのさまざまな機能を実行します。

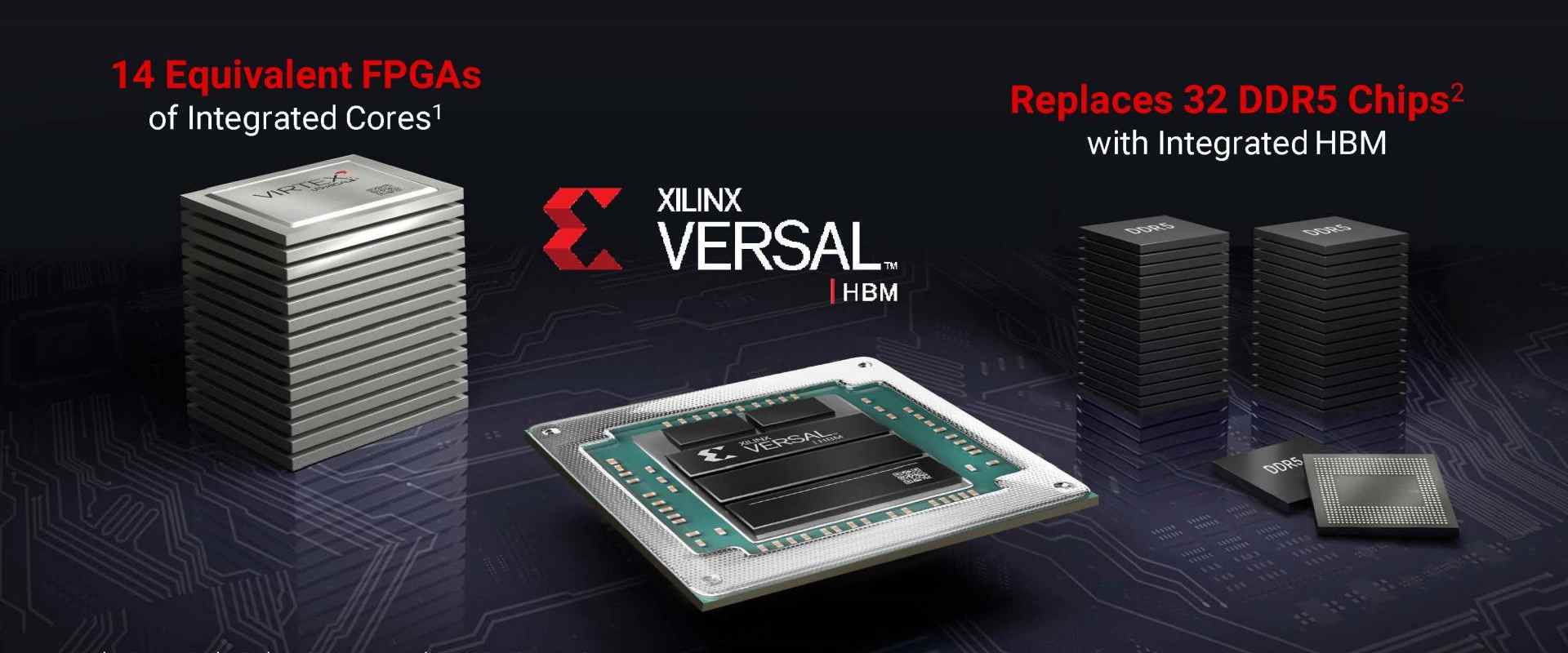

ザイリンクス バーサル

Xilinx Versal は、CPU、GPU、DSP、およびプログラマブル ロジックの機能を 1 つのデバイスに統合する ACAP ファミリです。 Versal は、データ センター、5G ワイヤレス、自動車分野における次世代アプリケーションの高性能と電力効率の要件を満たさなければなりません。

Versal デバイスは、FPGA とシステム オン チップ (SoC) を組み合わせた「アダプティブ コンピューティング アクセラレーション プラットフォーム」 (ACAP) として知られる新しいアーキテクチャに依存しています。 ACAP は、FPGA のプログラマビリティと柔軟性を、SoC の統合と使用の簡素化と組み合わせて、設計者が独自のハードウェア アクセラレータを作成し、システムを特定の要件に適合させることを可能にします。

Versal デバイスには、さまざまなアプリケーションの要求を満たすためにさまざまなサイズと構成があります。 このシリーズのデバイスには、最大 900 万個のシステム ロジック セル、6,840 個の DSP エンジン、および 8,520 個の AI エンジンが搭載されています。 Versal は、PCIe Gen 5 や DDR5 などのさまざまな高速接続もサポートしています。

Vitis 開発環境、Vivado デザイン スイート、およびザイリンクス ランタイム ライブラリは、Versal ベースのシステム (XRT) の作成を支援するためにザイリンクスが作成したソフトウェア ツールです。 さらに、同社は、ネットワーキング、ビデオおよび画像処理、機械学習など、Versal で使用するさまざまな IP コアを提供しています。

Xilinx Versalの設計プロセス

ザイリンクス Versal のようなシステムオンチップ (SoC) は、いくつかの形式のプログラマブル ロジック、CPU コア、メモリ、およびその他の IP ブロックを単一のチップ上に組み合わせています。 アーキテクチャ定義、システム レベル デザイン、IP 統合、機能検証、タイミング解析、物理デザインは、ザイリンクス Versal デザイン プロセスの一部の段階です。 この記事では、Xilinx Versal を設計する際のいくつかの困難とベスト プラクティスに加えて、各ステップを詳しく説明します。

アーキテクチャの定義

システムのアーキテクチャの定義は、設計プロセスの最初のステップです。 これには、システムの要件と仕様を評価し、適切な CPU コア、プログラマブル ロジック、メモリ、その他の IP ブロックを選択し、これらの要素を接続する方法を理解することが必要になります。 アーキテクチャを定義するときは、パフォーマンス、消費電力、サイズ、システム コストをすべて考慮する必要があります。

システムレベルの設計

さまざまな IP ブロック間のリンクを示す高レベルのシステム ブロック図の作成は、システム レベルの設計段階として知られています。 この図は全体的な設計の青写真として機能し、潜在的なパフォーマンス上の問題やボトルネックを特定するのに役立ちます。 この段階で、設計者は、システムがさまざまなゾーンにどのように分類されるか、およびデータがゾーン間でどのように移動するかについても考慮する必要があります。

IPの統合

システムレベルの設計が完了すると、設計者はさまざまな IP ブロックを設計に組み込むことができます。 これを実現するには、IP ブロックがシステムの仕様に準拠し、適切なインターフェイスに接続し、機能をテストする必要があります。 統合する必要のある IP ブロックが数百、さらには数千になる可能性があるため、この時点で設計の複雑さを管理することは、重大な困難の 1 つです。

機能検証

システムが予想どおりに動作し、設計要件を満たしていることを確認するプロセスは、機能検証として知られています。 さまざまな状況下でシステムの動作を模倣するテストベンチは、これを行う準備ができていなければなりません。 さらに、結果の正確性を確認する必要があります。 機能検証は、システムが意図したとおりに動作することを保証し、設計上の欠陥を早期に特定するのに役立つため、設計プロセスにおける重要なステップです。

タイミング解析

設計がシステムのタイミング要件に準拠しているかどうかは、タイミング解析によって確認されます。 これには、さまざまな IP ブロック間のタイミング接続を検査して、セットアップ、ホールド期間、およびクロック周波数が許容範囲内にあるかどうかを確認することが必要になります。 設計がタイミング仕様に準拠していない場合、機能上の問題やシステム パフォーマンスの低下が生じる可能性があるため、タイミング解析は非常に重要です。

物理設計

設計プロセスの最終段階である物理設計では、設計をシリコン上に配置します。 これには、チップを詳細にレイアウトし、さまざまな IP ブロックの配線と配置を計画し、設計が製造標準に準拠していることを確認するためにいくつかのチェックを実行することが必要になります。 さらに、物理設計では、パフォーマンス、消費電力、チップ サイズのバランスをとる必要がありますが、これは困難で時間のかかる手順です。

課題とベストプラクティス

ザイリンクス Versal の設計には、設計の複雑さの制御、システムがパフォーマンスと電力要件を確実に満たすこと、設計時間とコストの削減など、いくつかの問題が伴います。 ただし、設計者は次のベスト プラクティスに従うことで、これらの問題を克服できます。

トップダウンの設計アプローチを使用します。

この方法では、高レベルのシステム設計から始めて、手順の各段階で設計を改善する必要があります。 この戦略により、システムが要件を確実に満たしながら、設計エラーの可能性が低減されます。

IP ブロックを再利用します。

Xilinx Versal には、さまざまなデザインに役立つさまざまな IP ブロックが含まれています。 IP ブロックを再利用すると、設計の複雑さを最小限に抑え、時間を節約できます。

シミュレーションおよびエミュレーション ツールを使用します。

設計の欠陥は、シミュレーションおよびエミュレーション ツールを使用して、シリコンに設計を実装する前のプロセスの早い段階で発見されます。 これらのツールは、さまざまなシナリオでシステムのパフォーマンスと機能をテストすることもできます。

徹底的な機能検証を実行します。

設計プロセスの重要なステップである機能検証は、システムが意図したとおりに動作し、設計要件を満たしていることを確認するのに役立ちます。 設計者は、すべての潜在的なシナリオとエッジケースに対応する徹底的なテストベンチを開発する必要があります。

電力消費を最適化します:

Xilinx Versal には、動的な電圧と周波数のスケーリング、パワー ゲーティング、その他の電力最適化機能がすべて含まれています。 システムの電力使用量を削減するには、これらの特性を設計に組み込む必要があります。

タイミング クロージャに注意してください。

設計プロセスで最も困難な部分の 1 つは、タイミング クロージャです。 設計がシステムのタイミング要件を確実に満たすように、設計者はタイミング解析ツールを使用し、クロック ドメイン クロッシングやパイプライン化などの方法を使用して時間ルートを短縮する必要があります。

適切な設計慣行を使用します。

設計者は、モジュール設計、適切な命名規則、コードのコメントなど、健全な設計原則に従う必要があります。 これにより、設計の読みやすさ、保守性、再利用性が向上します。

他のデザイナーとコラボレーションする:

Xilinx Versal の作成は、さまざまなスキルを必要とする、複数の専門分野にまたがる困難な作業です。 たとえば、設計が要件を満たし、エラーがないことを確認するには、設計者は他の設計者、システム アーキテクト、検証エンジニアと協力する必要があります。

最後に、Xilinx Versal の設計には、アーキテクチャ仕様から物理設計までのいくつかのステップを含む、厳密で組織化された方法論が必要です。 それにもかかわらず、ベスト プラクティスに従うことで、設計者は障害を克服し、システムのパフォーマンス、電力、コストの要件を満たす高品質な設計を作成できます。

ザイリンクス Versal アーキテクチャ

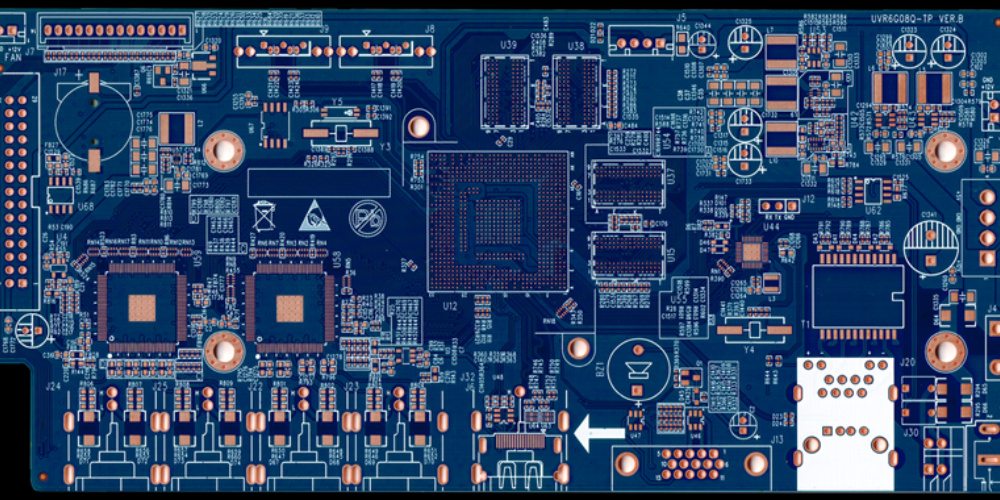

Xilinx Versal は、あらゆる種類のアプリケーション向けのカスタム ハードウェア アクセラレータの作成に使用できる素晴らしいプラットフォームです。 FPGA のパワーと柔軟性と、システムオンチップの容易さと統合を組み合わせています。 このプラットフォームは、CPU、DSP、プログラマブル ロジックなどの多くの処理エンジンを備え、すべて高速ネットワークに接続されている適応型コンピューティング アクセラレーション (ACAP) に依存しています。 これにより、優れたパフォーマンス、低遅延、低消費電力を備えた特殊なハードウェア アクセラレータを構築できます。 さらに、柔軟性が高く、ソフトウェア制御のエンジンとプログラマブル ロジックを通じてワークロードの変化に適応できます。 3 つの主要なコンポーネントは、プロセッサ サブシステム、プログラマブル ロジック サブシステム、およびプラットフォーム管理サブシステムです。

処理サブシステム

処理サブシステムは、Arm Cortex-A72 アプリケーション プロセッサ、Arm Cortex-R5 リアルタイム プロセッサ、Mali グラフィックス プロセッサ、その他のデジタル シグナル プロセッサ (DSP) などのいくつかの処理エンジンで構成されます。 NoC はこれらのエンジンを接続し、協力して困難なタスクを実行する場合があります。 プロセッサ サブシステムに含まれる他の周辺インターフェイスには、イーサネット、USB、PCIe、DDR メモリなどがあります。

その主な特徴の 1 つは、ワークロードに従ってリソースを動的に割り当てる処理サブシステムの能力です。 ハードウェア アクセラレータとソフトウェアによって制御される処理エンジンが連携してこれを実現します。 ソフトウェア制御の処理エンジンは、必要に応じてさまざまなタスクに柔軟に割り当てることができます。 対照的に、ハードウェア アクセラレータはプログラマブル ロジック サブシステムを利用するように設計されており、特定のタスクを調整できます。

プログラマブル ロジック サブシステム

ザイリンクス Versal プログラマブル ロジック サブシステムは、AI やその他のハイ パフォーマンス コンピューティング アプリケーションの作成と実装を促進します。 これは、Versal Adaptive Compute Acceleration Platform (ACAP) 上にあります。 高速相互接続、高度なネットワーキング、セキュリティ機能と、プログラマブル回路、ソフトウェアでプログラマブルな計算、およびメモリを組み合わせています。

プログラマブル ロジック サブシステムは、高度にプログラム可能でスケーラブルなプラットフォームを提供します。 これにより、プログラマは特定のアプリケーション要件に合わせてパフォーマンス、コスト、消費電力のバランスを取ることができます。 高速シリアル トランシーバーとプログラマブル I/O インターフェイスを備え、プログラマブル ロジック ブロック、DSP スライス、メモリ ブロックなどのさまざまなプログラマブル ロジック リソースも含まれています。

Versal ACAP プラットフォームは、さまざまなソフトウェア ツールとライブラリを提供します。 その結果、ハードウェア機能に加えて、アプリケーションの開発と展開も高速化されます。 これらには、AI Engine ソフトウェア開発キットが含まれます。 また、処理およびプログラマブル ロジック サブシステム用の統合されたソフトウェア開発フローも提供します。

プラットフォーム管理サブシステム

ザイリンクス Versal では、プラットフォーム管理サブシステムが電源管理、セキュリティ、システム レベルの操作を含むシステム全体を監視します。 セキュリティ処理ユニット (SPU)、システム管理ユニット (SMU)、および電源管理ユニットは、プラットフォーム管理サブシステム (PMU) を構成するさまざまな部分の一部です。

セキュリティ処理ユニット (SPU)

セキュリティ処理ユニット (SPU) として指定されたハードウェア コンポーネントは、ハードウェア ベースのセキュリティ機能の実行を担当します。 セキュア ブート、安全なキー ストレージ、安全なファームウェア アップグレードなどのいくつかのセキュリティ機能が SPU によって提供されます。 さらに、SPU は、不要なアクセスを回避するためにシステムの残りの部分から分離されており、システム全体に安全な基盤を提供できます。

SPU が提供する重要なセキュリティ機能は、セキュア ブートです。 セキュア ブートでは、ブート プロセス中に信頼できるソフトウェアのみがロードされるようになり、マルウェアやその他の不正なコードがシステム上で実行されるのを防ぎます。 ファームウェアとソフトウェア コンポーネントがブート プロセス全体でロードされると、SPU はそれらの信頼性と完全性を確認する信頼のチェーンを保存します。 さらに、いずれかのコンポーネントが検証に失敗すると、ブート プロセスが中断され、システムの起動が停止します。

暗号化と認証に必要な暗号キーを安全に保管するために、SPU も利用できます。 キーを安全に保管し、不正なアクセスを制限するために、SPU は特殊なハードウェアベースのキー管理を採用しています。 これにより、秘密キーやその他の重要な情報がハッカーから安全に保護されます。

システムが最新の安全なファームウェアを実行していることを確認するために、SPU は安全なファームウェアのアップデートも提供します。 さらに、SPU は、安全なチャネルを通じてファームウェアのアップデートをダウンロードして検証することにより、ハッカーによるファームウェアの改ざんを防ぎます。

システム管理ユニット (SMU)

システム管理ユニットは、ザイリンクス Versal デバイス (SMU) のシステム レベルのアクティビティを監視します。 SMU は、電源管理、温度管理、システム監視などのさまざまなシステム レベルの機能を提供します。

SMU の主な機能は電源管理です。 SMU は、システムの電力消費を管理し、さまざまなコンポーネントに電力が最も効率的に供給されるようにする役割を果たします。 SMU で使用される省電力技術には、クロック ゲーティング、パワー ゲーティング、および動的電圧および周波数スケーリング (DVFS) が含まれます。

熱制御は、SMU によって利用可能になるもう 1 つの重要な機能です。 デバイスの温度は SMU によって監視されます。 また、許容可能な動作範囲内に維持されていることを確認する責任もあります。 SMU が温度を調整するには、ファン制御、動的なクロック周波数調整、サーマル スロットリングなどのいくつかの技術が不可欠です。

システム監視は、SMU が提供するもう 1 つの重要な機能です。 電圧、温度、クロック周波数などのシステムの健全性と状態は、SMU によって監視されます。 システム管理者がシステムを監視および管理するために SMU が提供する監視インターフェイスには、JTAG、SMBus、および IPMI があります。

Xilinx Versal と以前のザイリンクス アーキテクチャとの比較

最新のザイリンクス アーキテクチャであるザイリンクス Versal は、以前のザイリンクス アーキテクチャからの大きな変更点を示しています。 ザイリンクス Versal と以前のザイリンクス アーキテクチャの重要な違いは次のとおりです。

統合:

ザイリンクス Versal と以前のザイリンクス システムとの最大の違いは、統合の度合いです。 ザイリンクス Versal は、複数のプロセッシング ユニット、プログラマブル ロジック、メモリ、IO を 1 つのユニットに組み合わせたプラットフォームとして完全に統合されます。 対照的に、以前のザイリンクス アーキテクチャは、処理とプログラマブル ロジックを別個のデバイスに依存していたため、より複雑なシステム デザインが必要となり、より多くの電力を消費しました。

柔軟性

Versal は、以前のザイリンクス アーキテクチャよりも優れた柔軟性を備えています。 幅広い I/O 規格、メモリ インターフェイス、接続オプションをサポートしているため、多くのシステムとの統合が簡単になります。 さらに、Dynamic Function eXchange (DFX) も提供します。 この機能により、必要に応じてプロセッシング コアを追加または削除するなど、変化するニーズに合わせて単一のデバイスを変更できるようになります。

消費電力の削減:

Versal は電力効率に重点を置いています。 高度な電源管理、改善された電圧制御、パフォーマンスを犠牲にすることなく電力使用量を削減する適応型電力スケーリングなどのさまざまな機能を備えています。

ハイパフォーマンス

Versal は、以前のザイリンクス アーキテクチャと比較して、はるかに優れたパフォーマンスを提供します。 コンピューティング集約型のアプリケーション、高速ネットワーキング、複雑な AI/ML ワークロードの要求に対処できます。 パフォーマンスを強化する機能には、保護されたコンピューティング エンジン、高速相互接続、高帯域幅メモリが含まれます。

統合されたシステムオンチップ (SoC) 機能:

Versal は、従来の FPGA ファブリックと追加のオンチップ要素を組み合わせています。 これらには、統合されたシステムオンチップ (SoC) 機能を作成するために、Arm プロセッサ コア、メモリ、通信が含まれています。 その統合により効率が向上し、プロセッシング コアとプログラマブル ロジックを必要とするシステムの構築が容易になります。

接続性:

Ethernet、PCIe Gen4、CCIX は、ザイリンクス Versal が提供する高速接続オプションのほんの一部です。 このプラットフォームは、多くの周辺機器やその他のデバイスに迅速に接続できるため、さまざまなアプリケーションに役立ちます。

全体として、Xilinx Versal は、さまざまなアプリケーションやワークロードにわたって優れたパフォーマンスを備えた適応性の高いプラットフォームであるため、開発者やシステム設計者にとって魅力的なオプションです。